制造商:英特尔(中国)有限公司

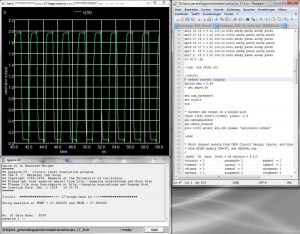

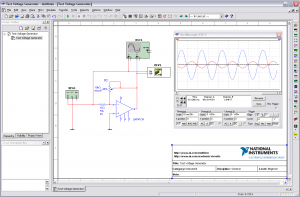

DSP构建器为英特尔®FPGAs是一个数字信号处理(DSP)设计工具,使硬件描述语言(HDL)生成DSP算法直接从数学工作模拟*环境到Intel英特尔®FPGAs。

该工具从MATLAB函数和模拟链接模型生成高质量的、可合成的VHDL/虚拟日志代码。生成的寄存器传输级别(RTL)代码可用于Intel®FPGA编程。针对英特尔®FPGAs的DSP构建器被广泛应用于雷达设计、无线和有线通信设计、医学成像和电机控制应用中。

特点

针对Intel®FPGAs的DSP生成器能够实现具有高性能和高效的高性能的DSP设计。以下是一些突出显示的功能:

将RTL导入到您的数学作品*MATLAB/模拟链接环境中,以进行协同模拟和代码生成。

从高级原理图到针对Intel®fpga的低级优化VHDL。

利用矢量处理进行高性能的固定点和浮点数字信号处理(DSP),如复杂的IEEE 754单精度浮点处理。

在英特尔®Arria®10和英特尔®分层®10设备中,执行按钮设计迁移到英特尔的硬浮点DSP块。

从具有ALU折叠的平面数据速率设计构建自定义算术逻辑单元(ALU)处理器架构。

执行高级合成优化,自动管道插入和平衡,以及目标硬件映射。

使用灵活的“白盒”快速傅里叶变换(FFT)工具包构建定制的快速傅里叶变换(FFT)算法,该工具包具有开放的库和块的层次结构。

使用设计者指定的系统时钟约束来自动设置管道、时分多路复用/折叠和关闭计时。

访问高级数学。h函数和多通道数据。

为没有Intel®Quartus®Prime软件编译的所有设计生成资源利用率表。

自动生成项目或脚本的英特尔®Quartus®主要软件,时间分析器,平台设计器(原Qsys),和模型FPGA*-英特尔®FPGA版本。

21.3有什么新功能

DFT(离散傅里叶变换)块举例演示在5G无线中的应用。

读取(RA)控制内存块关闭时钟到内存,以减少功耗。FFT ip会在适当的情况下自动使用RA功能。

减少了背靠背DSP生成器功能功能的开销。

DSP构建器专业版支持英特尔®旋风®V(编译生成RTL与四英质标准)。

独立安装DSP构建器来创建和模拟DSP构建器模型,并生成RTL(与Quartus相关的特性不可用)。稍后通过设置环境变量将四英奏连接到DSP生成器。

暂无评论内容