制造商:上海概伦电子股份有限公司

NavisPro是一个针对功耗、时序优化的RTL设计规划解决方案,它可以预测和预防设计中出现物理实现问题。它提供的SoC设计规划解决方案是在设计的早期阶段寻找最佳的电源PAD数和位置,以满足目标压降和同步开关噪声(SSN)裕度。NavisPro使设计者最大程度的减少设计迭代以缩短SoC设计的上市时间。它还将全芯片设计划分为多个子系统并实现层次化的布局规划,各子系统的版图都是独立实现的。在这种设计环境中,芯片划分包括设计的物理层次划分和各子系统的引脚放置。子系统的引脚布局是子系统版图的关键约束之一,它决定了全芯片布线的质量。

在现代SoC设计中,许多处理器被用在单个芯片中。子系统间总线互连时序的准确估计是时序收敛的关键。跨设计层次的接口网络时序估计对于全芯片级接口网络时序是非常有用的。

产品优势

Navis-FP

以约束驱动的RTL布局

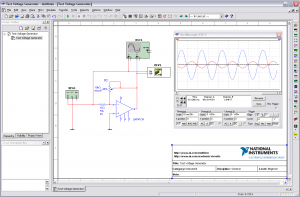

灵活的封装设计分析

快速进行设计迭代

Navis-CM

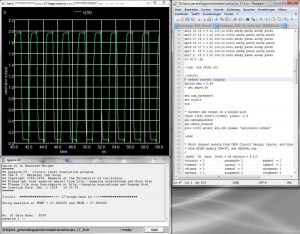

可视化RTL设计和调试

可视化的时钟树结构和时钟设计规则检查

图形化调试环境的电源约束验证和校正

设计早期阶段的设计约束管理

产品应用

SoC设计的RTL阶段布局可行性分析

用于倒装贴片式封装芯片设计的带凸点的IO PAD配置

RTL和门级逻辑电路设计

© 版权声明

文章版权归作者所有,未经允许请勿转载。

THE END