制造商:上海思尔芯技术股份有限公司

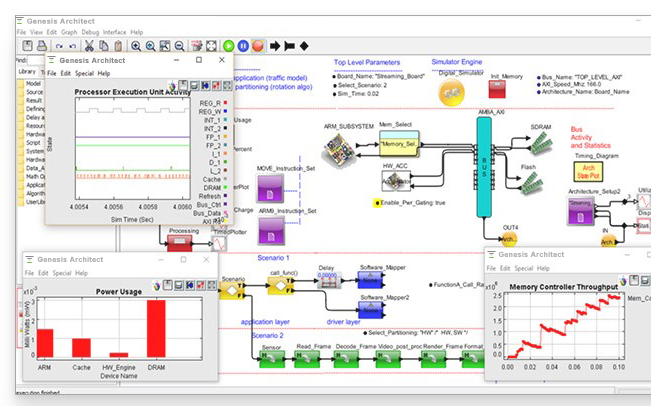

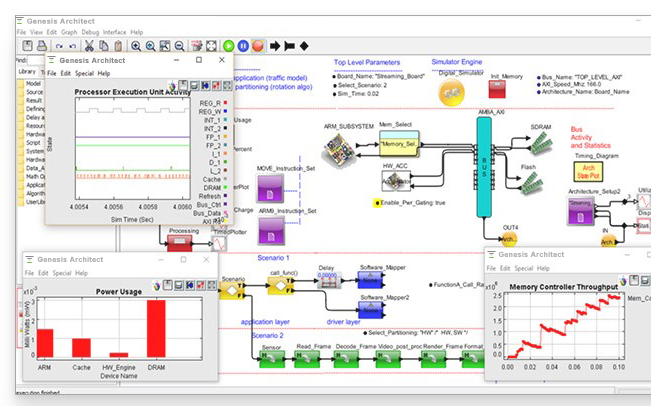

Genesis Architect 是 S2C 的架构设计产品,涉及系统设备、应用软件、半导体芯片、人工智能、网络通信、信号处理和控制系统等领域都可用此产品进行架构开发和优化设计。

系统工程师,架构师,设计师和验证工程师可以通过整合 C 或 RTL 代码、附加工具产生测试用例的方式,进行硬件在环(HiL)仿真,来开发和验证规范的实施,达到验证最终产品的目的。

Genesis Architect 架构设计平台主要特点如下:

图形化开发与软件接口(graphical development and interfaces)

-

操作界面由四个模型构建选项组成,这些选项可灵活地选择实现方式:框图,有限状态机,脚本编辑器和编程。

-

软件接口集成在Genesis Achitecture 的仿真器内。支持包括与硬件,工具和 FPGA 板的跟踪文件,文本文件导入/导出、数据报,SystemC,MatLab/Simulink,C/C ++/Java/Python 代码等接口信息和其他 XML 接口

多域、多层次(multi-domain)

-

计算模型包含:离散事件,同步数据流,连续时间,有限状态机和 SystemC

-

类和动态实例化:框图,代码,脚本和 FSM 可以构建为独立的块并按层次进行搭建。对独立模块的更改后其他引用它们的任何模型也将立即产生更新。

-

通过 Genesis Architect,可构建较多具有 300 个层次的模型;可设置网络中所有的使用者共享所有模型。

内建模型库

-

大型的基本建模组件库,包括事件激励生成器,文件读取器和写入器,变量和参数管理,数学运算符,算法,绘图,显示和排列;

-

符合行业标准的技术 IP 模型库,例如处理器,内存,缓存,总线,接口,DMA,网络,软件任务和 RTOS。这些 IP 与 Genesis Architect 框图编辑器集成在一个界面,使用者可以快速建模。

XML 数据库

-

使用开放的 DTD(Document Type Definition)格式,并可用自定义脚本轻松地从其他工具(例如 SysML)导入/导出。由于引用了其他 XML 文件且只是可读,只记载模型的文件特定项的改变,所以文件比较小。

调试平台

-

带有模型执行情况的图表型调试,监听器,缓冲区使用情况和利用率的可视化报告,断点设置便于设置存储模型中间状态的检查点。

报告生成器

-

提供 500 多个用户配置报告,包括延迟,吞吐量,利用率,缓冲区占用,退出/进入数,功耗,峰值功率,功率/设备,功率/任务,累积功率,命中率,失速时间和服务质量

服务器/PC 需求

-

Genesis Architect 可跨平台操作,需要的硬盘空间不大于 1GB,仅需大约 2GB 的内存即可运行;一般大型模型约占用 3MB 硬盘空间

Genesis Architect 使用者界面

Genesis Architect提供多层次建模的图形界面的设计环境,具有开放的 DTD XML 数据库,多域仿真,提供与第三方工具、语言和仿真器的接口。

Genesis Architect 附带了大量的建模组件,技术 IP 块和工具,用于开发完整的自定义组件/子系统。设计者使用模型库可以快速构建模型,利用适当的计算模型进行仿真,生成的报告进行分析。为了支持精确建模,程序框图编辑器具有错误检测和报告,语法检查器,图形调试器,跟踪和日志记录。创新的库管理功能可以使世界各地的建模平台之间共享子系统,并集成到版本控制软件中。

Genesis Architect 可用于研究系统的性能,功耗,功能和信号正确性。产品套件可识别设计过程中难以发现的问题区域,用户能够尝试各种可能属性的组合,权衡功率性能、功能后优化产品设计。

Genesis Architect 支持多种建模方法,用户可以选择最适合其开发和应用的一种方法。所用方法的示例包括 Y 图表,用例到体系结构映射,网络流建模和软件/硬件分割。