制造商:

Scientific Analog软件是一款应用于大规模及超大规模数模混合电路设计的软件,使用Scientific Analog可以快速完成模拟电路的建模以及数模混合电路的系统仿真,使得模拟电路设计像数字电路一样方便快速,可以大幅的提升设计效率和准确率。

Scientific Analog软件可以帮助客户完成Top-down或者Bottom-Up的设计流程,工程师不需要写代码就能轻松完成模拟电路的建模,降低模拟电路的设计难度,更为客户节省人工与周期成本。

XMODEL

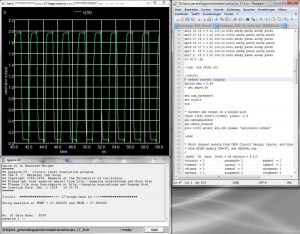

XMODEL是应用于Verilog中的模拟建模与仿真。

XMODEL提供了非常丰富且参数化的原语库,包括功能级原语和电路级原语。因此工程师完全不需要编程,只需要像搭积木一样,将原语组合就能构成模型和测试平台。另外,客户还可以用原语库创建自己的器件模型库。

利用XMODEL内置的原语可以快速高效的完成模型搭建,并利用基于事件驱动仿真器在SystermVerilog完成仿真。计算速度比Verilog- AMS或Real-Number Verilog要快10-100倍以上

GLISTER

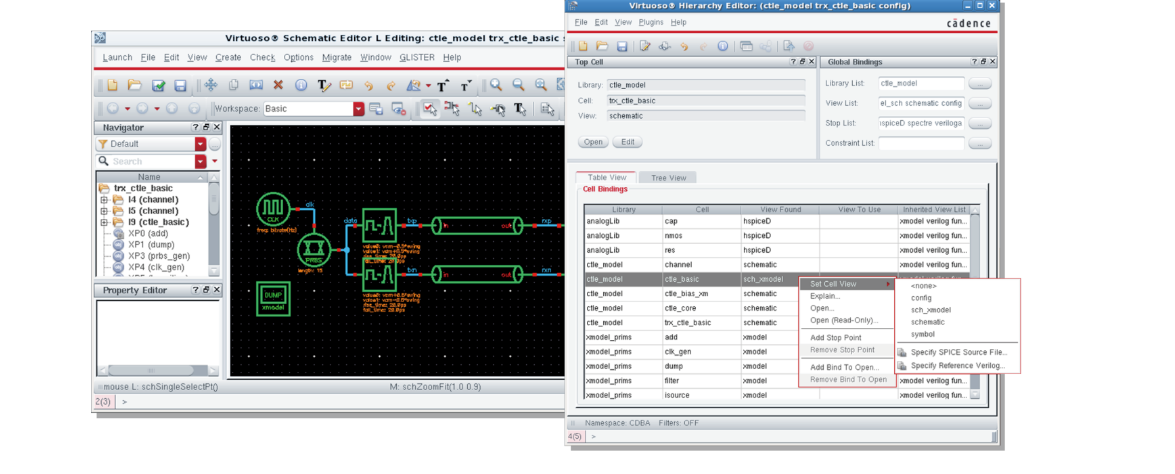

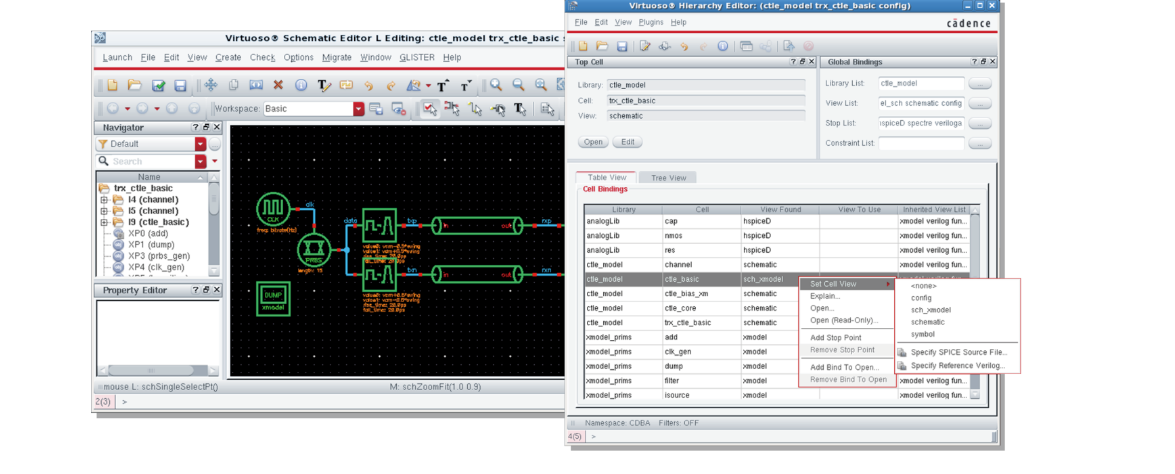

GLISTER—与Virtuoso集成,应用于原理图(Schematics)中的电路模型。

GLISTER完全集成与Cadence Virtuoso设计环境,是将XMODEL与MODELZEN完全界面化和图形化,用原理图(Schematic)图形符号来表示XMODEL原语。这样客户用GLISTER就不再需要编写代码,只需将这些图形通过任意组合就可以生成模型,产生模型后可以直接进行XMODEL仿真。

当在hierarchy中既有电路原语又有其他spcie模型时,就需要做XMODEL-SPICE联合仿真。GLISTER可以协助XMODEL进行联合仿真:

- GLISTER可以提供必需的SystemVerilog模型文件、SPICE/Spectre网表和混合信号仿真控制文件;

- 通过cadence Hierarchy editor可以选取cell或instance;

- GLISTER Testbench测试台为Synopsys的VCS和XA和Cadence的NCVerilog和APS等仿真器提供统一的接口;

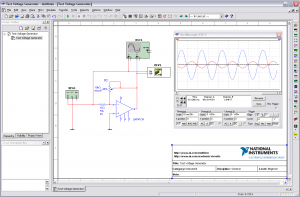

MODELZEN

MODELZEN的主要功能是从电路中自动提取生成模拟模型。MODELZEN利用XMODEL丰富的电路原语优势,可以将任意的电路转换为等效的SystemVerilog模型。

暂无评论内容