制造商:Cadence Design Systems

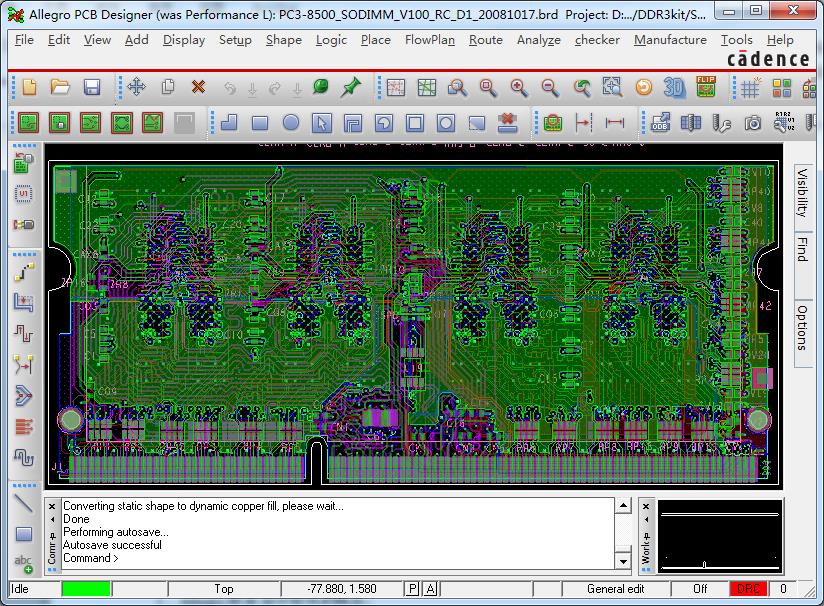

Allegro是Cadence推出的先进 PCB 设计布线工具。 Allegro 提供了良好且交互的工作接口和强大完善的功能,和它前端产品Cadence OrCAD Capture的结合,为当前高速、高密度、多层的复杂 PCB 设计布线提供了最完整解决方案。

Allegro PCB Designer是一个可扩展的,经过验证的PCB设计环境,在解决技术和方法的挑战同时,可以使设计周期可控并尽可能缩短。Allegro PCB Designer解决方案采用了基础软件加选项的配置方案,包含了与PCB设计相关的一个完整的设计流程所需的一切。基础软件即Allegro PCBDesigner——包括一个共同的一致的约束管理器(constraint management)解决方案,PCB Editor,自动/交互式布线器,以及用于制造和机械CAD的接口。PCB Editor提供了一个完整的布局和布线的环境——从基础平面规划,布局和布线到布局复制高级互联规划,分别针对简单或复杂的PCB设计。

- 提供一个经过验证、可扩展的,高性价比的PCB编辑和布线解决方案以及按需升级的配置方案。

- 通过约束驱动的PCB设计流程,避免不必要的反复。

- 支持对物理,间距,面向制造、组装和测试的设计(DFX),高密度互连(HDI),和电气(高速)域设置一个全面的规则。

- 包含一个从前端到后端的、共同的、一致的约束管理系统,用于约束条件的创建、管理和确认。

- 提供第三方应用的开放环境,可以提高工作效率,同时成为更佳综合工具。

Allegro PCB PI

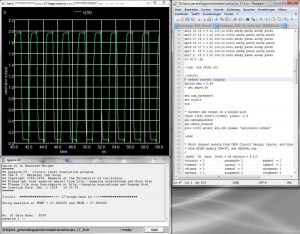

Allegro PCB PI Option XL是Allegro PCB SI XL附加的可选项,Allegro PCB PI Option是一个综合设计和分析为一体的开发环境,可以分析电源噪声和高速PCB的电源分配系统设计。它包含了高速电路电源分配系统的频率特性设计优化技术。 用于设计和优化的高频特性(提供回路阻抗)的电源系统中的高速电路板设计。它提供了一个完整的设计分析环境,给用户简单快速的做迭代式“change-simulate-analyze”在短时间内。Allegro PCB PI是建立在Allegro PCB SI XL上的,给用户提供一个完整的SI和PI设计和分析环境。工程师现在可以修改电源传输系统通过简单的SI和PI分析,并容易获得模拟引擎的信号完整性和电源完整性。PCB PI XL直接采用Allegro layout数据库(.brd)避免了数据转换的需求,用Allegro PCB PI Option XL module的用户不必再定义一些必须的仿真环境参数,如:层机构stackup和电源层属性,Allegro PCB PI Option XL提供一个的,整合设计和仿真分析一体的开发环境,它包含频域分析,信号完整性分析和Allegro PCB设计环境,用户可以在前期设计中对单点做“what-if”分析从而达到设计阻抗匹配和正确选择耦合电容,当耦合电容位置确定时,用户就可以对设计做多点分析来评估电容布局效果计算设计自感系数,Allegro PCB PI Option XL提供一个独特的电源系统设计流程,它具有一个完整的逐步查错的步骤,点选波形可以在PCB中高亮显示网络。提供一个终端向导,可以帮你选择终端电阻电容等,指导你做元件布局,从等到一个更好的电源分配系统。

功能特征:

- 用户启动新的设计可以使用安装向导

- 板框

- 层叠构

- 电源平面分割

- 对称电源地平面

- 设置电源DC网络

- 电容封装库使用等等。电源完整性(PI)和信号完整性(SI)的综合设计和分析环境

- 频域分析引擎单节点(简单快速)和多节点(复杂,更准确地)模拟与物理布局设计环境

- VRM输入电容电感计算

- 去耦电容和阻抗计算

- 自带高速电容封装库

- 添加/修改编辑电容模型

Cadence Allegro PCB SI

Cadence PCB信号和电源完整性

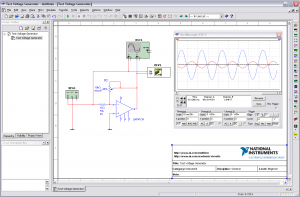

Cadence PCB信号完整性 (SI) 和电源完整性技术(PI)提供了可调整、高性价比并且支持前仿真和后仿真的系统互联设计和分析环境。Cadence PCB SI和PI产品与Cadence Allegro PCB编辑器、Allegro PCB布线器、 Allegro Design Entry HDL和Allegro System Architect紧密结合,能够实现冲前端到后端、约束驱动的高速PCB系统设计。

Cadence PCB SI技术让设计师嫩够在整个设计过程中解决高速问题、从而能够解决高密度、高复杂度和高速边沿变化率等不断提高的挑战带来的问题。通过这种方法,设计团队不需要在设计过程的后期进行耗时耗力的仿真——修复——再仿真的反复验证。它还让设计团队在更大化系统电气性能的同时最小化成品的总成本。除了支持Cadence DML建模外,IBIS建模标准也已经原生支持,而晶体管级模型可以通过原生的Spice仿真器以及一个向导来执行导入。另外,工程师可以通过将生产容差加入拓扑仿真来提高产量(成品率)。

Cadence PCB SI技术集成的设计和分析环境使的设计师不再需要转换设计数据库进行仿真。设计师还可通过考虑封装设计对芯片间传输的信号整体表现的影响,从而更精确地解决时序预算的问题。此设计流程让设计师能够轻松执行对复杂的高速PCB系统布线前和布线后的模型提取与仿真验针。

优势

- 高度集成的设计和分析环境避免设计转换带来的错误和时间消耗。

- 简单易用的布线前分析(前仿真)工具引入了一个设计方法,可以通过一致的、从前端到后端的约束管理系统简化布线后的设计验证。

- 电源稳定性和供给可以通过DC和AC电源分析得以优化。

- 串行设计方法支持采用前仿真和后仿真的方式,通过使用更新的业界标准IBIS-AMI模型执行快速、精确而且详细的超大码长仿真,从而指导设计。

- 复杂的源同步并行接口的时序预算可以使用优化的总线分析解决方案有效地确认。

Allegro PCB Design HDL

Allegro PCB Design L 与Allegro Design Entry HDL的组合构成一个完整的PCB设计解决方案。它包含了下面的一些工具和功能:Allegro Design Entry HDL,用于解决混合电路层级的原理图设计,同时支持行为级与结构描述两种方式。Allegro PCB Editor,一个功能全面的交互式PCB版图编辑器,可以支持较多256个信号层的PCB设计。Allegro PCB Router ,一个基于形状的自动交互式的布线器,限于6层信号以内的同步布线,并且具有宽泛的接口支持,包括AutoCAD DXF, IDF, PADS & P-CAD数据转换。设计数据库通过CAE Views (API)和EDIF3.0.0工具进行访问. 原理图的网表接口提供非独有格式的ASCII文件输入/输出。一个全面的VERILOG仿真模型库被用来描述TTL, CMOS ECL, Memory, GaAs以及接口等常用组件。组件库生成环境包含库的浏览和Allegro Design Entry HDL下的组件生成以及针对PCB组件生成的librarian functionality高级开发功能。

![图片[1]-Allegro PCB Designer-卡核](http://www.caxkernel.com/wp-content/uploads/2023/04/20230422094057-6443aba978b10.jpg)

暂无评论内容