制造商:Mentor Graphics

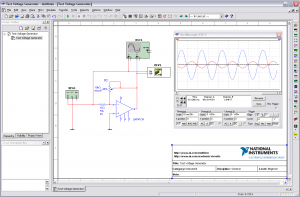

ModelSim 可模拟行为、RTL 和门级代码 – 通过独立于平台的编译提高设计质量和调试效率。单内核模拟器技术可在一个设计中实现 VHDL 和 Verilog 的透明混合。

ModelSim特色

ModelSim 可模拟行为、RTL 和门级代码 – 通过独立于平台的编译提高设计质量和调试效率。单内核模拟器技术可在一个设计中实现 VHDL 和 Verilog 的透明混合。

快速完成覆盖

高级代码覆盖率

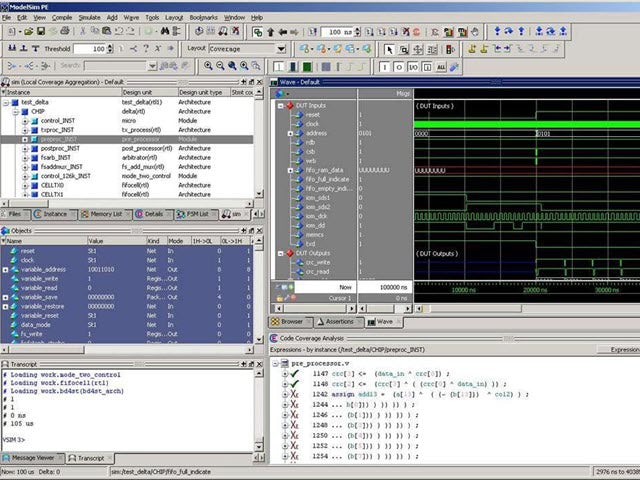

ModelSim 的高级代码覆盖率功能为系统验证提供了有价值的指标。此外,ModelSim的易用性降低了利用验证资源的障碍。所有覆盖范围信息都存储在高效的UCDB数据库中。覆盖结果可以通过交互方式、仿真后或合并多个仿真运行后查看。

混合语言模拟

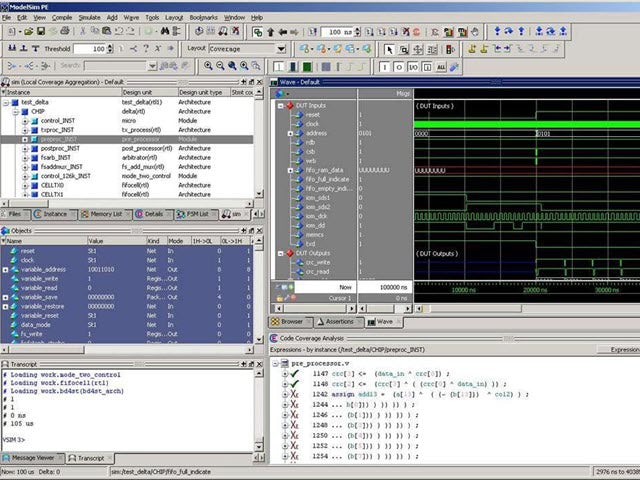

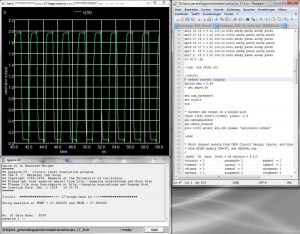

对 Verilog、SystemVerilog for Design、VHDL 和 SystemC 的全面支持为单语言和多语言设计验证环境提供了坚实的基础。易于使用的统一环境为FPGA设计人员提供了调试和仿真所需的高级功能。

快速调试

直观的调试环境

ModelSim 通过智能设计的调试环境简化了查找设计缺陷的过程,该环境可有效地显示设计数据,以便对所有硬件描述语言进行分析和调试。Verilog、VHDL 和 SystemC 的广泛直观功能使其成为 ASIC 和 FPGA 设计的理想选择。

© 版权声明

文章版权归作者所有,未经允许请勿转载。

THE END

暂无评论内容