制造商:Cadence Design Systems

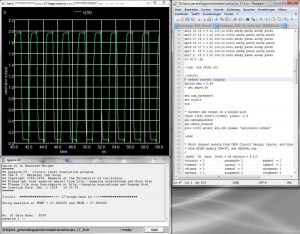

Verilog HDL(简称 Verilog )是一种硬件描述语言,用于数字电路的系统设计。可对算法级、门级、开关级等多种抽象设计层次进行建模。Verilog 继承了 C 语言的多种操作符和结构,与另一种硬件描述语言 VHDL 相比,语法不是很严格,代码更加简洁,更容易上手。Verilog 不仅定义了语法,还对语法结构都定义了清晰的仿真语义。因此,Verilog 编写的数字模型就能够使用 Verilog 仿真器进行验证。

主要特性

下面是 Verilog 的主要特性:

- 可采用 3 种不同的方式进行设计建模:行为级描述——使用过程化结构建模;数据流描述——使用连续赋值语句建模;结构化方式——使用门和模块例化语句描述。

- 两类数据类型:线网(wire)数据类型与寄存器(reg)数据类型,线网表示物理元件之间的连线,寄存器表示抽象的数据存储元件。

- 能够描述层次设计,可使用模块实例化描述任何层次。

- 用户定义原语(UDP)创建十分灵活。原语既可以是组合逻辑,也可以是时序逻辑。

- 可提供显示语言结构指定设计中的指定端口到端口的时延,以及路径时延和时序检查。

- Verilog 支持其他编程语言接口(PLI)进行进一步扩展。PLI 允许外部函数访问 Verilog 模块内部信息,为仿真提供了更加丰富的测试方法。

- 同一语言可用于生成模拟激励和指定测试的约束条件。

- 设计逻辑功能时,设计者可不用关心不影响逻辑功能的因素,例如工艺、温度等。

主要应用

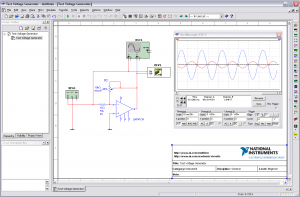

专用集成电路(ASIC),就是具有专门用途和特殊功能的独立集成电路器件。Verilog 作为硬件描述语言,主要用来生成专用集成电路。

主要通过 3 个途径来完成:

1、可编程逻辑器件

FPGA 和 CPLD 是实现这一途径的主流器件。他们直接面向用户,具有极大的灵活性和通用性,实现快捷,测试方便,开发效率高而成本较低。

2、半定制或全定制 ASIC

通俗来讲,就是利用 Verilog 来设计具有某种特殊功能的专用芯片。根据基本单元工艺的差异,又可分为门阵列 ASIC,标准单元 ASIC,全定制 ASIC。

3、混合 ASIC

主要指既具有面向用户的 FPGA 可编程逻辑功能和逻辑资源,同时也含有可方便调用和配置的硬件标准单元模块,如CPU,RAM,锁相环,乘法器等。

© 版权声明

文章版权归作者所有,未经允许请勿转载。

THE END

暂无评论内容