制造商:Cadence Design Systems

Cadence® PSpice® A/D是一款功能齐全的模拟电路仿真器,支持数字元件。它可轻松与Cadence PCB原理图输入解决方案集成,并带有易于使用的图形用户界面,为用户提供完整的设计流程,以帮助解决从高频系统到低功耗IC设计的几乎任何设计挑战。由于其广泛流行,具有内置数学函数和行为建模技术的PSpice模型可从许多IC供应商处获得。

软件功能

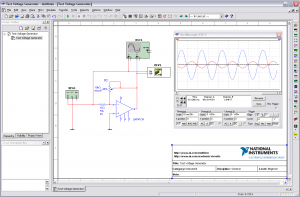

混合模拟/数字仿真

通过 PSpice® A/D 和 Cadence 前端 PCB 设计的无缝集成,提供用于 PCB 设计和仿真的统一设计环境。访问包含超过 33,000 个符号和模型的大型数据库,以便使用 Cadence PCB 原理图设计输入工具进行仿真设计。

- 设置和运行来自 OrCAD 捕获的模拟和交叉探测模拟结果。直接在原理图上查看仿真偏置结果,包括节点电压、引脚和子电路电流以及器件功耗计算。

- 将分层网表与参数化子电路结合使用,以更快地将复杂的分层设计网表化

- 扩展的仿真可以在后台运行,同时继续进行设计编辑

- 创建多个仿真配置文件并将其保存在 OrCAD 捕获项目管理器中,以便调用和运行以前的仿真

- 在仿真和原理图设计输入工具之间无缝转换。

模拟环境

统一的仿真环境提供了以下功能:

- 执行和监控仿真,查看和编辑文本文件,查看仿真消息和图形结果。

- 利用模拟分析功能,如用户定义的精度、自动时间步长控制和专有收敛算法来控制仿真过程

- 通过在瞬态分析的非关键时段放宽容差和时间步长,或将瞬态分析扩展到预先指定的结束时间之外,以交互方式权衡精度和仿真时间

- 抢占当前模拟以立即运行另一个模拟,然后返回以在稍后完成抢占模拟;控制等待执行的模拟队列

调试和收敛

调试和融合功能包括

- CHECKPOINT RESTART:通过在不同时间点存储模拟状态,然后从任何模拟状态重新启动模拟来节省时间。在从预先记录的时间状态开始仿真之前,您可以修改仿真设置和设计参数。

- 自动收敛:自动更改容差收敛极限,使设计收敛。您可以使用此选项获得收敛,然后通过进一步修改模拟器选项来微调仿真。对于电力电子设计,建议使用此选项。

- 断言:使用特殊部分为模拟器插入错误和警告条件,以便在模拟过程中标记条件。

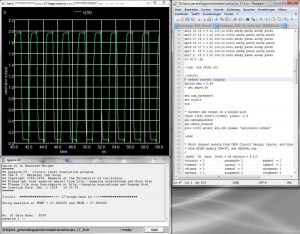

PSpice Probe

PSpice Probe允许用户从一组扩展的数学函数中进行选择,以应用于仿真输出变量。

- 在多个波形窗口中查看仿真结果

- 按名称或在原理图中标记网络、引脚或部件来选择波形

- 使用交叉探测标记一次,当您更改和重新仿真设计时,它们将一直与分析保持一致,标记的波形在每次仿真后都会显示

- 随着仿真的进行,查看连续、实时的“行进波形”

- 将高分辨率、可扩展的波形复制并粘贴到其他应用程序中,以生成文档

- 创建绘图窗口模板,并使用它们轻松绘制信号的复杂功能,只需在原理图中的所需引脚、网络和零件上放置标记即可

- 使用内置测量功能测量电路的性能特征,或创建自己的测量

内置模型

种类繁多的内置模型为仿真增加了灵活性,其中大多数包括温度效应

出厂型号包括 R、L、C,以及:

- 内置 IGBT

- 多种 MOSFET 型号,包括行业标准 BSIM4、BSIM3v3 和新的 EKV2.6 型号

- 五种GaAsFET晶体管型号,包括派克-斯凯伦和三小汤姆3型号

- BJT模型,包括Gummel Poon和Mextram

- 具有饱和和滞的非线性磁性模型

- 包含延迟、反射、损耗、色散和串扰的传输线模型

- 数字基元,包括具有模拟 I/O 型号的双向传输门

模型和建模

大型模拟和混合信号模型库,包括参数化模型和器件方程式开发人员工具包 (DEDK),用于实现新的和自定义的内部模型方程式。

- 从 33,000 多种模拟和混合信号型号的工业设备中进行选择

- 超过 4,500 种参数化模型,适用于BJT、JFET、MOSFET、IGBT、SCR、磁芯和环形线圈、功率二极管和电桥、运算放大器、光耦合器、稳压器、PWM控制器、乘法器、定时器和采样保持器。这些模型允许从原理图编辑器中将仿真参数作为属性传递

- 访问基本元件以及适用于更复杂器件的各种宏模型,包括运算放大器、比较器、稳压器、光耦合器、ADC 和 DAC

- 使用状态空间平均模型对开关模式电源进行快速可行性仿真和控制环路分析

- 为“模型编辑器”创建的模型自动生成 OrCAD 捕获零件

© 版权声明

文章版权归作者所有,未经允许请勿转载。

THE END

暂无评论内容