制造商:Cadence Design Systems

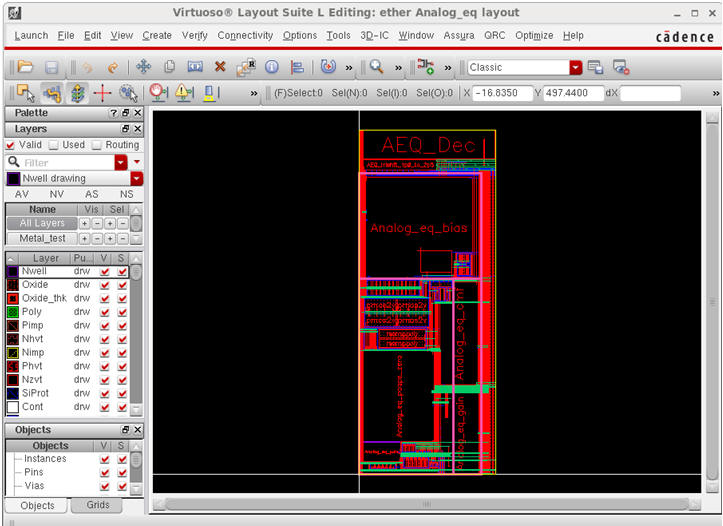

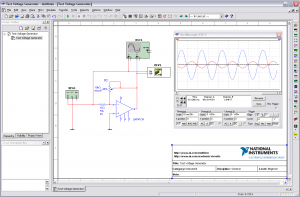

Cadence Virtuoso平台的完整定制IC布局套件,Virtuoso布局套件支持器件、单元、模块和芯片级别的定制模拟、数字和混合信号设计。增强的 Virtuoso 布局套件可加速性能和工作效率,从高级全自定义多边形编辑 (L) 到更灵活的原理图驱动和约束驱动的辅助全自定义布局 (XL),再到完全自定义布局自动化 (GXL)。Virtuoso布局套件与Virtuoso原理图编辑器和Virtuoso模拟设计环境无缝集成,可以创建快速且硅精度的差异化定制芯片。®

VIRTUOSO LAYOUT SUITE L

| 全阶层式、多窗式的设计环境 |

| Virtuoso Layout Suite L可在一个编辑环境中同时开启多个cells或blocks甚或是阶层均可在同一窗口打开,帮助设计者在复杂的设计中确认其数据的完整性,其整合的World Viewer全窗口可以很直觉地查看整个设计中相应区块的位置,并可执行选取、显示范围调整、重绘等常用指令,以提升布线效率。 |

| 多样的参数式Cells 加速设计时效减少设计错误 |

| Parameterized cells (Pcells) 提供设计自动化的效能以减少繁琐及重复的布图工作,Pcells可在不更动最原始cell的情况下更改每个cell 的尺寸、SHAPE及所含对象,依参数设定所建立、编辑和管理的shapes和devices可更加简化,以加速布图效率并减少设计错误。 |

| QuickCell选单自动建立Device |

| QuickCell (QCells) 参数选单功能可快速建立及编辑Pcells devices,可在无Pcells SKILL的环境下实现建立及编辑devices的环境, 由于QCells是 “C” 为基础的环境,所以可程序的Pcells SKILL也可套用及兼容于QCells 的环境下。 |

| 设计规范管控以增加效率 |

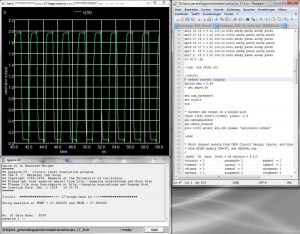

| Virtuoso Layout Suite提供 “设计规范管控”的功能,可以实时监控违反规范的错误,以增加布图效率减少错误点及侦错的时间,也支持90奈米(或更小)的各种复杂制程规范的technology file。 |

| 自动简化及优化的布线效果 |

| Virtuoso Layout Suite能够自动简化及优化block来达到以”设计规范管控”的功能和流程,“动态量测”省掉许多手动量测的麻烦,”对齐功能”也能加快对齐图型、接点和对象的效率,”讯号标示”让您在多阶的设计中达成对讯号查询,明亮显示及检查接续性目的。 |

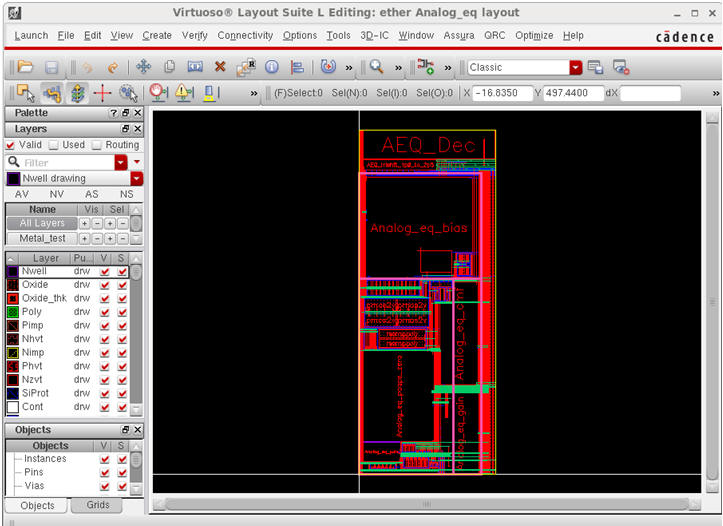

Virtuoso Layout Suite XL

Virtuoso 平台上更先进的定制布局环境,提供了constraint-driven 规范-管控及线路图-管控的两种实体布局环境,让您在设计数字、混和讯号及模拟产品时的device、cell和block阶都能有更好的规范可依循。

作为Virtuoso 的高阶布图平台,Virtuoso Layout Suite XL除了L 阶的基本polygon布图编辑功能之外,更针对device、cell 及block来提供定制数字、混和讯号和模拟设计等支持,也使得规范管控及设计管控的功能能够与其他自动化的进阶功能相结合,以加速定制零件编写的速度,别忘了还有parameterized cell (Pcell) 和 SKILL 可让您在device的建立和编辑时更能得心应手。

© 版权声明

文章版权归作者所有,未经允许请勿转载。

THE END

暂无评论内容