制造商:Mentor Graphics

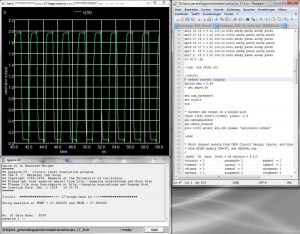

FPGA I/O优化可以消除FPGA和PCB设计组织之间的障碍,以更高的精度和速度实现并行设计过程,并提供正确的按结构FPGA I/O分配,允许在PCB过程中进行管脚交换和基于布局的I/O优化

FPGA I/O优化

FPGA设备的强大功能、灵活性和即时可用性创造了引人注目的业务驱动因素,这引发了FPGA在系统PCB设计实施中的大量采用。很明显,FPGA器件的上市时间优势和容量/性能特点已经实现了一个可行的替代方案,以替代资本资源更密集的定制IC/ASIC解决方案,以及在系统设计创建中成功整合标准“现成”组件的承诺。

好处:

桥接基于HDL的FPGA设计和PCB设计领域,实现自动化、快速和无错误的双向数据交换

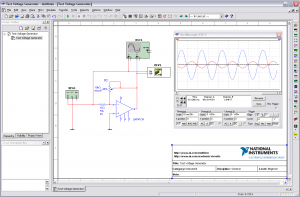

全集成、易于使用的多FPGA板上I/O优化减少了层数、成本和设计时间

通过构造正确的FPGA供应商规则驱动的I/O分配将重新旋转最小化

快速、简单且自动化的FPGA符号生成节省了数天的PCB设计创建时间

利用标准企业库中的FPGA符号进行快速、无错误的I/O优化

技术规格:

支持Altera、Xilinx、Lattice和Microsemi的更新FPGA供应商设备,以更大限度地减少安装时间并消除手动错误

按需服务保证更新的设备支持,通常不超过14天

基于实际PCB布局组件方向的双向I/O优化和引脚交换

针对每个设备的内置I/O分配规则,简化了引脚分配

使用公司库中的通用FPGA符号/符号集,或允许您为特定FPGA设计创建自定义集

管理流之间的数据一致性,自动生成更新的FPGA位置和路由约束

集成式楼层规划器允许优化工程师桌面上的FPGA I/O,以改进布局和布线

使用成熟的技术,跨多个FPGA设备进行优化,从而获得更好的结果

与Xpedition Enterprise和PADS专业流程紧密集成,在设计过程中的任何时候都可以访问和优化

暂无评论内容