制造商:

软件主要特点:

– 内建单内核仿真器支持SystemVerilog、Verilog、VHDL、PSL以及SystemC。

– 内建约束解释器支持Constrained-random激励生成,以实现Testbench-Automation;

– 支持基于PSL,SystemVerilog语言断言的功能验证,支持业界最著名的0-in Checkware 断言库功能验证

– 集成化支持功能覆盖率检查与分析

– 高性能的RTL和Gate-level仿真速度

– 支持用SystemVerilog和SystemC实现高层次testbench设计与调试

– 高性能集成化的混合语言调试环境加速对混合验证语言;(SystemVerilog,SystemC,PSL,VHDL,Verilog)的交叉调试与分析

– 基于标准的解决方案能支持所有的流程,便于保护验证上的投资

– 提供最高性价比的功能验证解决方案

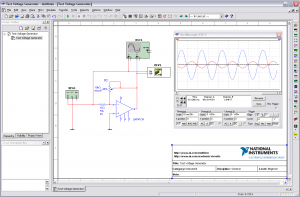

Questa AFV提供真正的混合语言验证功能

Questa AFV是以混合语言流程 (mixed language flow) 为目标的单核心验证解决方案,它同时支持SystemVerilog、VHDL、PSL和SystemC,使设计人员能够选择合适的语言。除此之外,与SystemVerilog验证能力的紧密连结,并将其用于受限随机(constrainedrandom)测试平台的产生以及功能覆盖率的验证也对VHDL使用者大有好处。QuestaSim用户界面与ModelSim类似,命令也完全兼容。

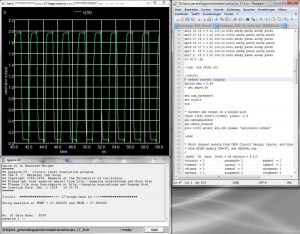

Questa提供测试代码覆盖率Coverage)检查功能

Questa的DPI Use流程支持

代码覆盖率快速收敛技术

Questa CoverCheck显著提升了实现代码覆盖率收敛的进程。即使在完成完备的仿真验证后,通常仍然会有一些没有被覆盖的代码。CoverCheck可以定位这些问题,帮助使用者决定是否要忽略这段代码或者加强测试环境直至其被测到。

基于Formal形式化技术,不需任何Testbench与断言

与Questa无缝连接,支持UCDB;

可更早发现覆盖率漏洞;

智能引导设计者加速代码覆盖率收敛;

完全自动化的流程;

良好的图形化分析界面。

CoverCheck在仿真完成后,读取保存在统一覆盖率数据库(UCDB)中的代码覆盖率结果,然后使用形式化方法来特别定位无法探查的代码。一种可能性是:CoverCheck可以证明目标代码实际上完全不会被执行。另一种可能性是:如果代码能被形式化方法探查到,则CoverCheck通过显示激励波形,给设计者提供必要的指导以加强其编写测试向量并在下次的仿真中检查这一部分设计。CoverCheck通过形式化技术标记仿真中难以探查的代码覆盖率,因此其提供了一个有价值的验证方法。CoverCheck既可以作为独立的形式化验证工具工作,也可以与动态仿真工具在Questa高级验证。

暂无评论内容