制造商:深圳鸿芯微纳技术有限公司

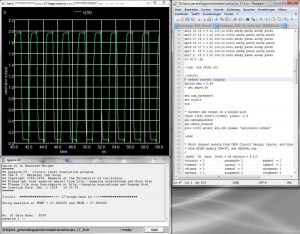

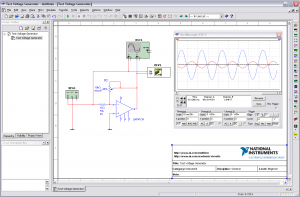

Aguda是深圳鸿芯微纳技术有限公司的布局布线工具软件,也是目前国内唯一能够提供完备的数字集成电路物理设计解决方案的国产EDA工具,从Netlist-In 到GDS-Out完整的电子设计自动化流程,涵盖从布局、预布线、布局优化、时钟树综合、时钟树优化、详细布线、顶层集成的全部技术。

• 以布线为中心的技术构架 – 该构架让布局布线过程中绕线层、绕线模式、拥塞、Pin连接等关键步骤变得更为有效,大幅减少迭代的次数,从而加速设计收敛的时间;

• 自适应MCMM(Multi-Corner Multi-Mode)技术 – 在布局布线过程中,动态自动选择时序最差的签核场景进行优化,极大地减少签核阶段的ECO次数;

• 高度一致的签核时序分析能力 – 内置的时序分析引擎提供与STA工具完美的一致性,所有的时序优化都基于更优的QoR进行,原生支持:

◇ AOCV,SBOCV,SOCV和LVF

◇ 等多种片上偏差模型;

◇ 基于图形和路径的分析与优化方法;

◇ 先进的信号完整性和噪声分析能力;

• Color-Aware的DPT布线技术 – 独创的Color-Aware布线专利,能够完美处理先进制程下DPT(Double-Pattern-Technology)的设计规则;

• 层次内的优化技术(in-Hierarchy-Optimization)– iHO优化技术,可以在顶层时序优化的同时,对子模块及边界时序进行优化,避免多次时序优化迭代,及不必要的平坦化设计,大大降低内存消耗,同时将时间成本从数周降到数天;

• 预知拥塞的低电阻(Low-R)布线技术 – 在布局优化阶段精确地预估拥塞和时序,将高层低电阻金属预留给关键路径布线,优化时序,提升性能;

• 一体化的时钟/数据优化技术 – 同时进行时钟路径和数据路径的优化,在MCMM的场景下提升性能和降低功耗;支持多种结构的时钟树,如H树,多点树,以及网格树;

• 电压降和电迁徙预知的布局布线技术 – 在布局布线阶段自动检测并规避潜在的电压降风险,同时支持先进工艺节点的电迁徙规则,在布线的过程中检测并自动修复;

• 低功耗驱动的优化技术 – 原生支持UPF和CPF格式的低功耗约束文件,可同时优化静态功耗和动态功耗;

• 广泛的工艺节点支持 – 支持多家半导体厂商的主流及先进工艺制程;

• 功能完备的模块级布局布线工具,内嵌的强大分析引擎在布局布线的每个技术环节提供实现和优化,得到更优的物理设计结果;工具支持业界标准的输入和输出数据格式,如Verilog,SDC,LEF/DEF,标准单元库,GDSII文件。

• 完整的自上而下层次化顶层设计工具,在芯片级布局规划和顶层集成的技术中,共享同一时序、布局和布线的工具引擎,在提供更优的时序一致性基础上,也为复杂的芯片项目提供无缝的数字设计集成环境;

• 独有的以布线为中心的技术构架,以及统一的层次化数据库,使得设计效率提升两倍;

• 得益于特有的专利技术,在获取25%的性能提升基础上,能得到15%的功耗降低和10%的芯片面积缩小;

• 所有设计环节支持多线程和分布式计算,快速便捷地获得设计效率提升;

• 友好的工具界面和脚本支持,用户能够在现有流程中快速导入和部署鸿芯微纳的物理实现解决方案;

• 支持标准输入输出格式,与签核工具高度一致的时序分析引擎;