制造商:Silvaco中国

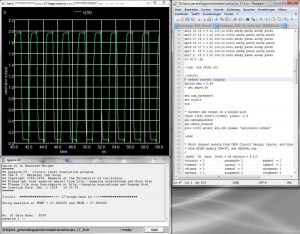

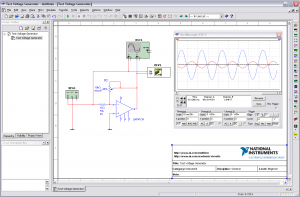

Guardian对模拟、混合信号和RF IC设计执行交互式和批处理模式验证,它与Silvaco原理图捕获和版图编辑器集成。Guardian有效地执行设计规则检查(DRC)、版图网表提取和版图与原理图(LVS)的比较。

• Guardian优化用于64-bit Linux系统

• 与Expert版图编辑器和Gateway原理图编辑器紧密集成,为模拟、混合信号和RF射频设计提供完整的

从输入到验证的设计流程

• 支持由Dracula™和Diva™转换的DRC/LVS/NET规则文件

• 支持晶圆代工厂(Foundry)认证的工艺设计套件(PDK), 被广泛应用于半导体工艺技术。

• 快速直观的分层式LVS调试程序,具备版图和原理图之间交叉探测的功能

• Guardian NET支持应力效应和邻近参数提取

• Silvaco强大的加密功能可以用来保护客户和第三方的知识产权

Guardian DRC主要特征:

易用性:

• 与许多领先的DRC工具兼容

• 安装简单,无需咨询技术人员即可设置环境

• 图形和文本格式的DRC错误报告提供导航和视图化,对新老用户都相当直观

高效、多功能:

• 完备的DRC命令集适用于任何设计环境——局部 DRC命令用于交互式环境,全芯片DRC命令则用于批处理环境

• 基于高效内存管理和先进算法,优化的层操作从Windows和Linux平台上获得更佳性能

• 基于连接性的DRC操作包括天线规则检查(antenna rule checking)

• 使用基于图形任务处理方法优化执行DRC命令

精准、快速、大容量:

• 支持90度、45度、以及任意角度图形,而丝毫不影响模拟和混和信号设计版图的精度

• 交互式DRC在Expert版图编辑器中运行,提供局部区域快速DRC,并可将错误存储于芯片错误数据库中,从而保持局部错误数据库与芯片错误数据库的一致性

• 分层式DRC报告数据库可追踪DRC运行历史纪录

• 分层式DRC错误报告功能更大化了版图调试效率

• 多线程DRC可显著提高性能和容量

Guardian LVS/NET特点:

易用性:

• 直观的分层式LVS差异报告可显著缩短除错调试时间

• Gateway原理图编辑器与Expert版图编辑器的数据库直接链接,可提供交叉探测,即时生成图形差异报告

• 子电路的黑盒子选项提供了分层模式中的渐进式LVS比较,并可将IP模块轻松纳于高层验证设计 之中

精准、快速、大容量:

• 可精确计算尺寸相关的SPICE参数,这些参数对于含有默认或用户定自义公式的模拟设计非常重要

• 可在LVS追踪中精确识别通用器件(如晶体管、 二极管、电阻、电容等)、用户自定义器件和/或黑盒子电路

• 可对性能不匹配的任何半导体工艺,有效提取全芯片版图网表

高效、多功能:

• 分层式设计数据库支持平展式式和分层式LVS网表比较

• 可处理器件成型中所用到的任意形状的多边形

• 可更大程度地保留原始层次,以便于轻松调试版图后仿真( postlayoutsimulation)

• 分层交叉探测原理网表、提取的版图网表、原理图设计、以及物理版图

• 可检测电气规则检查( ERC: Electrical Rule Check) 的违例状况( 如短路、开路、悬空和 连接不当的器件等),并具有方便的过滤选项功能

• 支持MOSFET、BJT、JFET、MESFET、Diode、 电阻、电容和参数化用户自定义器件

• 标注版图,其中的节点信息可启用在Expert IC设计环境中的先进功能,如节点探测、节点搜索、和短路查找器等。

• 多线程比较分层网表