制造商:Silvaco中国

Spider是一个网表至GDSII的布局和布线设计流程,用于主流的物理设计与实现。

Spider 主要特征

- 物理设计流程附带n层设计性能,确保流片所需的扩展性和灵活性

- 直接数据库系统带来高级性能,允许自由进行“动态(on-the-fly)” 查看和编辑设计数据以及参数,而不需费时地导入数据及导出格式转换

- 综合支持业界标准格式,可集成第三方工具和历史数据

- 工具内部的整体布局规划和混合信号支持,包括自动布局和进行“假设”分析,使得设计师可早期估计时间和区域,提供可预测的设计闭合

- 布局优化功能, 如自动网长度最小化和时序驱动算法,可优化单元布局

- Spider的自动化CTS特性,促成时钟树(CT)和高输出网路(HFN)的综合

- 对具有成本效益的服务器群进行深亚微米(DSM)时序驱动布线

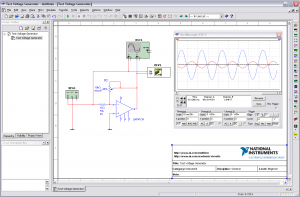

- 电容电阻和时序提取结合了嵌入SPICE和RC提取引擎,而不需外部工具

物理设计流程

- n层设计性能的物理版图

- 用户可定义参数配合版图生成代码特性

- 支持栅极阵列,结构ASIC和标准单元SoC设计样式

- 协助控制设计进程的方方面面

- 高亮凸现网路,以便于查看

高级性能以及电容电阻和时序提取

- 直接数据库允许自由查看和编辑设计数据及参数,而不需费时的输入和输出

- Self-Checking Correct-by-Construction方法不必外部检查,即可警告潜在问题

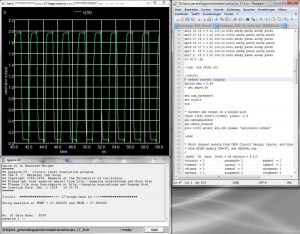

- GUI和命令行接口“重播”脚本,用于运行时间自动化

- 嵌入SPICE和电容电阻提取引擎

综合支持

- 自动合成缓冲区和逆变器,以帮助时序收敛

- 通过时序驱动Verilog和基于DEF流程与外部第三方的逻辑和物理综合工具集成

- 导入Verilog网表、SDC/SDF时序限制和Liberty .lib 时序模型

- LEF / DEF物理和技术库及设计交换格式支持

整体布局规划

- 配合多个物理单元类型的自动布局和“假设”分析

- 实时网表驱动的版图和ECO工艺确保无错误的连接性控制,附带在线独立验证和修改工具

- 内置网表、限制、库和数据库检查以及修改工具确保有效的布局和布线的初始条件和更新

- 逻辑层次网表管理,附带自动设计分区和区域控制布置

- 焊垫框架生成,以及芯片和宏电源的布置与生成

- 自动估计利用率和屏幕纵横比控制

- 布局和布线障碍控制特性,包括支持直线性

- 在布局过程中显示的加权精细线(flyline),允许放置组块来正确地最小化稠密现象

布局优化

- 自动网长度最小化和时序驱动算法优化单元布局

- 二维布局拥塞图

- 尺寸和/或实例控制束

- 可编程放置策略允许混合自由模式和类似数据路径单元放置方法

自动化CTS

- 启动时钟树(CT)和高输出网路(HFN)综合

- 自动优化插入延迟、斜率和时钟间斜率

- 提供延迟、转变、斜率和加载网路细节

布线

- 执行自动标准化单元和焊垫框架布线

- 通过SDF前向标注和Synopsys™net timing 控制文件支持时序驱动布线

- 支持深亚微米(DSM)设计规则

- 实时设计规则驱使的版图和ECO工艺确保无错误的几何设计,附带在线独立验证和修正工具

- 标注指定网表用于高级自动撤销(rip-up) 和重新布线,而不用完全重新运行和/或在整个设计或区域上布线

- 可编程的自动轮廓线、嵌入块、圆环、条形和rail布线可简便电源和接地设计及编辑

- 配合高级放置和布线编辑器,简易执行交互式编辑,不论是电源、接地或者信号网路

- 在布线期间,简便迅速地吸附、选择、分割、移动、添加拐角以及修改层次

简便易用性

- 简便“假设”布局规划分析功能以及自动版图生成器

- 强大的UPI和脚本功能,可创建宏和高级定制自动化环境,以及宏自动化来简便重复的任务

- 在设计流程的任何时候,均可简便替换单元和更新网表

- 带有对象吸附(object snapping)(重力)的简化的顶部组装和布局

- 接口 –script,macros and GUI

- 输入/输出 – GDSII, EDIF, verilog, LEF, DEF, Liberty .lib, SPICE, DSPF

© 版权声明

文章版权归作者所有,未经允许请勿转载。

THE END