制造商:Silvaco中国

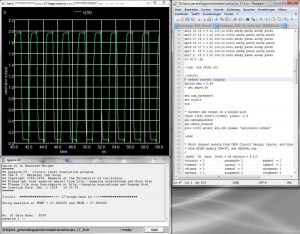

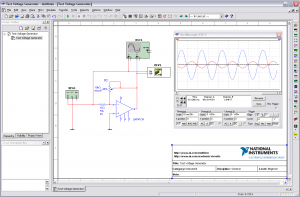

HIPEX是一个精确快速的全芯片分层提取软件,用于从分层电路版图中提取寄生电容和电阻。HIPEX与Expert版图编辑器紧密集成,用于电容电阻(RC)寄生参数的提取, 并配合DRC/LVS, 完成完整的设计验证流程。

特点:

• 含多个寄生参数提取模型, 包括集总电容电阻提取、仅电容提取、仅电阻提取、耦合电容提取,以及全分布式电容电阻提取

• 可选择特定网路进行提取,用于SoCs和大型内存中关键网路的电容电阻的快速提取

• 具有针对分布式寄生RC网络的高效网络约简功能

• 所导出的寄生参数网表(netlist)文件 包括SPICE格式、可反向标注的网表格式、 DSPF和SPEF格式

• 参数的自动反标注功能可不断完善电路版图的后仿真精确度与分析

• 不仅对管级电路, Hipex对门级电路也可进行寄生器件提取

HIPEX-NET器件提取:

• 与Expert版图编辑器相集成

• 可转换Dracula技术文件

• 在Solaris、Linux和Windows不同平台上,使用一致的图形用户界面(GUI)

• 在保存原始版图层次的基础上,提取分层式电路连线表,以便于分析

• 可提取MOSFET、MESFET、BJT、JFET、 diode、电容、电阻和参数化用户自定义器件

• 可执行针对短路、开路和悬空的电气规则检查(ERC)

• 可精确提取非45度和非90度的器件

• 高效的内存管理可处理大型设计

• 有32bit和64bit版本可供使用

• HIPEX-NET为非多线程

HIPEX-C寄生电容提取:

• 由基于规则的技术文件驱动

• 以寄生电容来反标注原理图网表

• Striping算法和stripe数据库可实现多个多处理器的高效并行运行

• 可提取全芯片和所选网路的寄生耦合电容

• 提供用户自定义或内置的电容模型来折衷精确度和运行时间

• 支持由EXACT生成的外部电容规则文件,以用于3D精准模式

• 按各个网路逐个提取的方式(net-by-net ),创建递增电容数据库

• 可选择特定网路进行提取,用于快速计算关键路径的寄生电容

HIPEX寄生电阻提取:

• 由基于规则的技术文件驱动

• 以寄生电阻来反标注原理图网表

• 可对接触提取寄生电阻值

• 可用于L型、T型、交叉和弯曲等各种形状的电阻

• 使用接触扩大化和接触集群化来简化寄生电阻的形态

• 针对全芯片和所选节点,分层提取带有寄生电容的网表

• 按各个网路逐个提取的方式(net-by-net ),创建递增电阻数据库

• 多个提取模型和方程解算器可用于任意形状的电阻

• 可分割长导电,以得到更精确的RC分布

• 将所选节点导出至GDS或CIF文件,以用于版图调试

HIPEX寄生网络分布

• 可将所提取的电阻与新建立的节点及寄生电容相结合

• 用户可自定义最小电阻和电容阈值

• 利用XY坐标,将电容精确地分布于寄生电阻上

• 在RC网络使用PI模型

• 结果输出至SPICE、DSPF和SPEF网表

• 用寄生电阻和电容来反标注原理图网表

• 以耦合模式导出分布式的寄生电容

HIPEX-CRC网络约简工具

• 显著的缩短了版图后仿真(post-layout)和布线后仿真(post-route) 的运行时间

• 通过去除悬空RC元件和阈值低于用户所定义的值的RC元件、合并并联电路/串联电路,以及基于散射参数的宏建模方式来进行网络约简

• 以线性时间来约简网络

• 可处理带有回路的RC网络

• 约简后的RC网络具有与原电路相同的仿真精确度

• 支持SPICE、DSPF或SPEF格式

• 使用了LISA脚本语言的定制约简算法可用于选择子电路、单

元、网路和阈值

暂无评论内容