制造商:英特尔(中国)有限公司

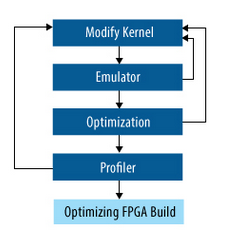

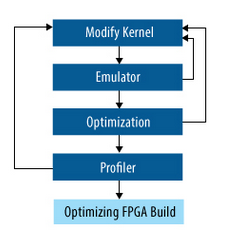

使用面向开放计算语言 (OpenCL™) 的 Altera® SDK,用户可以抽象出传统的硬件 FPGA 开发流程,采用更快、更高层面的软件开发流程。在基于 x86 的主机上迅速完成 OpenCL 加速器代码仿真,获得详细的优化报告,包括专门的算法流水线相关信息,缩短编译时间,直至得到满意的内核代码结果。利用预先编写的最优 OpenCL 或者 RTL 功能,从主程序调用它们,或者直接从您的 OpenCL 内核调用它们。

什么是 OpenCL?

OpenCL 标准是第一个开放、免版税、统一的编程模型,能够在异构系统上加速算法实现。OpenCL 支持在不同的平台上使用基于 C 的编程语言来开发代码,例如,中央处理单元 (CPU)、图形处理单元 (GPU)、数字信号处理器 (DSP),以及现场可编程门阵列 (FPGA)。

对于软件工程师而言,OpenCL 是编程模型,对于系统规划人员而言则是一种方法。它基于标准 ANSI C (C99),扩展了并行功能。OpenCL还包括应用程序接口 (API),一般通过 PCI Express® 实现主机与硬件加速器的通信,或者一个内核与另一个没有主机控制的内核进行通信。除此之外,作为供应商扩展功能,Altera 还提供 I/O 通道 API,将数据从 10Gb 以太网等流 I/O 接口直接输入到内核中。OpenCL 的关键优势在于它是可移植、开放、免版税的标准,这也是它与专用编程模型的关键不同。

在 OpenCL 模型中,用户规划任务来控制队列,每个器件至少有一个队列。OpenCL 运行时功能会将数据并行任务分解成片,将其发送给器件中的处理单元。这是主机与任何硬件加速器进行通信的方法。由每一硬件加速器供应商抽象出供应商相关的内容。面向 OpenCL 的 Altera SDK 完成这一工作,并且符合 OpenCL 1.0 标准。

关于 OpenCL 1.0 标准的详细信息,请参考 Khronos 的OpenCL 规范。Khronos 集团的很多供应商都支持 OpenCL。如果需要了解其他信息,请访问http://www.khronos.org/opencl/。

什么是面向 OpenCL 的 Altera SDK?

面向 OpenCL 的 Altera SDK 抽象出复杂的 FPGA 设计,支持软件编程人员采用基于 ANSI C 语言的 OpenCL C 来编写硬件加速内核函数,并支持其他的 OpenCL 结构,方便了在 FPGA 上实现应用程序。作为我们 SDK 的一部分,我们提供全套工具让软件编程人员更快速的完成开发流程,这包括:

-

在 x86 上单步调试代码的仿真器,确保了正常工作。

-

详细的优化报告,以理解负载和存储内部循环的相关性。

-

显示内核内部性能的分析器,保证了正确的存储器合并以及无阻塞硬件流水线。

-

OpenCL 编译器,能够在一个步骤中对内核代码进行 300 次优化,产生整个 FPGA 镜像。

面向 OpenCL 的 Altera SDK 已经全面投产,使得 Altera 成为解决方案符合 OpenCL 规范的第一家 FPGA 公司。面向 OpenCL 的 Altera SDK 支持各种主 CPU,包括 SoC 器件中的嵌入式 ARM® Cortex®-A9 处理器内核、IBM Power 系列处理器以及标准 x86 CPU 等。面向 OpenCL 的 Altera SDK 在多个 FPGA 和多块电路板以及各种存储器目标上支持可扩展解决方案,例如,可进行顺序存储器访问的 DDR SDRAM,进行随机存储器访问的 QDR SRAM,或者支持低延时存储器访问的 FPGA 存储器。还支持半精度以及单精度和双精度浮点。